## SCOC

Ref : R&D-SOC-NT-292-V-ASTR

Issue : 0 Rev. : 2

Date : 18/06/2003

Page : i

### SPACEWIRE IP CORE SPECIFICATION AND ARCHITECTURE

|               | Name and Function | Date | Signature |

|---------------|-------------------|------|-----------|

| Prepared by   | Tam LE NGOC       |      |           |

| Verified by   | Marc LEFEBVRE     |      |           |

| Approved by   |                   |      |           |

| Authorised by | Marc SOUYRI       |      |           |

| Document type | Nb WBS | Keywords |

|---------------|--------|----------|

|               |        |          |

Ref : R&D-SOC-NT-292-V-ASTR

Issue : 0 Rev. : 2 Date : 18/06/2003

Page : ii

### **DOCUMENT CHANGE LOG**

| Issue/<br>Revision | Date     | Modification Nb | Modified pages | Observations                                                                                              |

|--------------------|----------|-----------------|----------------|-----------------------------------------------------------------------------------------------------------|

| 0/0                |          |                 |                | Creation                                                                                                  |

| 0/1                | 01/04/03 |                 | 14,20,21,22    | Adding error response and error interrupt if the TX AHB slave is accessed when the link is not connected. |

|                    |          |                 |                | Suppression of the "shall".                                                                               |

| 0/2                | 03/04/03 |                 | 34,20          | Adding TX clock selection.                                                                                |

|                    |          |                 |                | Adding complete packet reception interrupt.                                                               |

|                    |          |                 |                | Adding AHB FIFO full status.                                                                              |

|                    |          |                 |                |                                                                                                           |

|                    |          |                 |                |                                                                                                           |

|                    |          |                 |                |                                                                                                           |

### PAGE ISSUE RECORD

Issue of this document comprises the following pages at the issue shown

| Page | Issue/<br>Rev. |

|------|----------------|------|----------------|------|----------------|------|----------------|------|----------------|------|----------------|

| all  | 0/0            |      |                |      |                |      |                |      |                |      |                |

| all  | 0/1            |      |                |      |                |      |                |      |                |      |                |

| all  | 0/2            |      |                |      |                |      |                |      |                |      |                |

|      |                |      |                |      |                |      |                |      |                |      |                |

|      |                |      |                |      |                |      |                |      |                |      |                |

# SCOC

Ref :R&D-SOC-NT-292-V-ASTR

Issue : O rev. 2 Date : 18/06/2003

Page : 3

#### **TABLE OF CONTENTS**

| 1 | Sco   | pe                                                 | 7        |

|---|-------|----------------------------------------------------|----------|

|   | _     |                                                    |          |

| 2 | Doc   | cuments and acronyms                               |          |

|   | 2.1   | Applicable documents                               | 8        |

|   | 2.2   | Reference documents                                | 8        |

|   | 2.3   | Acronyms                                           | 8        |

| 3 | Fun   | nctional description                               | <i>9</i> |

|   | 3.1   | global functionality description                   | 9        |

|   | 3.1.1 |                                                    |          |

|   | 3.1.2 | 2 Introduction of the interfaces                   | 9        |

|   | 3.1.3 | B Link initialization                              | 10       |

|   | 3.1.4 | Transmission function                              | 10       |

|   | 3.1.5 | Reception function                                 | 10       |

|   | 3.2   | functional mode description                        | 11       |

|   | 3.3   | Detailed functionality description                 | 12       |

|   | 3.3.1 |                                                    |          |

|   | 3.3.2 | 2 TX Host Interface (THI)                          | 12       |

|   | 3.    | 3.2.1 TX DMA mode                                  | 12       |

|   | 3.    | 3.2.2 TX slave mode                                | 13       |

|   | 3.3.3 | RX Host Interface (RHI)                            | 14       |

|   | 3.    | 3.3.1 The format of the storage                    | 14       |

|   | 3.    | 3.3.2 The functionality of the RHI                 | 16       |

|   | 3.    | 3.3.3 Reaching the End_Packet Address              | 17       |

|   | 3.    | 3.3.4 Reaching the End_Area Address                | 17       |

|   | 3.    | 3.3.5 AHB error occurrence                         | 18       |

|   | 3.    | 3.3.6 Advice                                       | 18       |

|   | 3.3.4 | Format of the words stored in the TX and RX FIFOs: | 18       |

|   | 3.3.5 | The interrupts                                     | 18       |

|   | 3.3.6 | Time Code transmission and reception               | 19       |

|   | 3.3.7 | 7 Test mode                                        | 19       |

|   | 3.4   | Internal register description                      | 20       |

|   | 3.4.1 | Global description                                 | 20       |

|   | 3.4.2 | 2 Detailed description                             | 21       |

|   | 3.5   | Interface description                              | 28       |

|   | 3.5.1 | Clocks, test and reset                             | 28       |

|   | 3.5.2 | 2 APB interface                                    | 28       |

|   | 3.5.3 | TX AHB master interface                            | 28       |

|   | 3.5.4 | TX AHB slave interface                             | 29       |

## SCOC

Ref :R&D-SOC-NT-292-V-ASTR

Issue: O rev. 2 Date : 18/06/2003

Page: 4

|     | 3.5.5    | RX AHB master interface         | 30 |

|-----|----------|---------------------------------|----|

|     | 3.5.6    | Link interface                  | 30 |

|     | 3.5.7    | Time interface                  | 30 |

|     | 3.5.8    | Interrupt interface             | 30 |

| 4   | Peri     | formance                        | 31 |

| 5   | Arci     | hitecture description           | 32 |

|     | 5.1      | Description of the reset trees  | 33 |

|     | 5.2      | Blocks working at TX clock      | 34 |

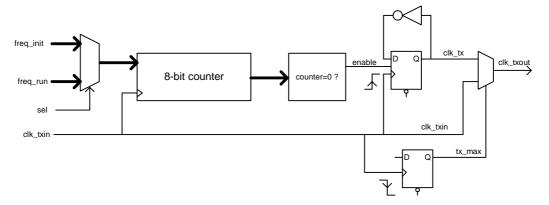

|     | 5.2.1    | CLK_TX_GEN block                | 34 |

|     | 5.2.2    | DS_GEN block                    | 34 |

|     | 5.2.3    | TX_SHIFT_REG block              | 34 |

|     | 5.2.4    | TX_SELECT block                 | 35 |

|     | 5.2.5    | TX_CNT block                    | 36 |

|     | 5.2.6    | TX_ACK block                    | 36 |

|     | 5.2.7    | TX_RESYNC block                 | 37 |

|     | 5.3      | Blocks working at RX clock      | 38 |

|     | 5.3.1    | RX_SHIFTREG block               | 38 |

|     | 5.3.2    | RX_DECOD block                  | 39 |

|     | 5.3.3    | RX_RESYNC block                 | 40 |

|     | 5.       | 3.3.1 DISCONNECTION block       | 40 |

|     | 5.4      | Blocks working at system clock  | 41 |

|     | 5.4.1    | INIT_FSM block                  | 41 |

|     | 5.4.2    | DELAY_CNT block                 | 42 |

|     | 5.4.3    | RX_MGT block                    | 42 |

|     | 5.4.4    | RX_FIFO block                   | 43 |

|     | 5.4.5    | TX_FIFO block                   | 43 |

|     | 5.4.6    | AHB_FIFO block                  | 43 |

|     | 5.4.7    | TX_MGT block                    | 44 |

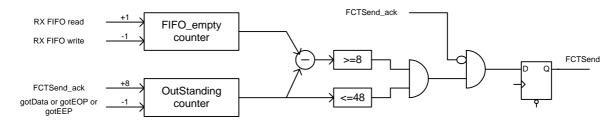

|     | 5.4.8    | SW_COUNTERS block               | 45 |

|     | 5.4.9    | SW_RESYNC block                 | 46 |

|     | 5.4.1    | 0 SW_REG block                  | 47 |

|     | 5.4.1    | 1 AHB_TX_INT block              | 49 |

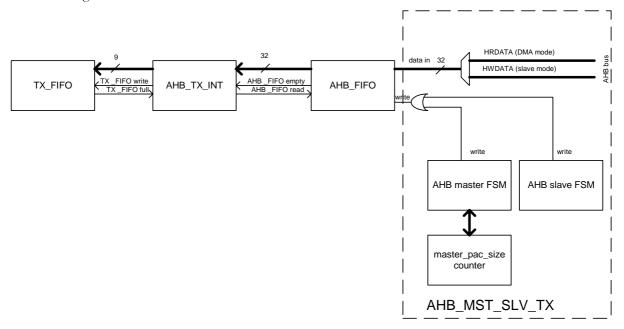

|     | 5.4.1    | 2 AHB_MST_SLV_TX block          | 51 |

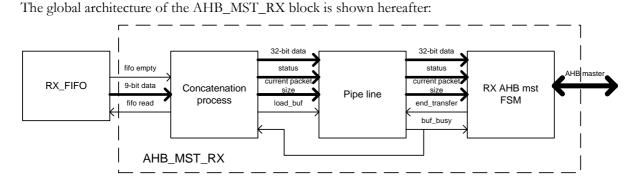

|     | 5.4.1    | 3 AHB_MST_RX block              | 56 |

|     | 5.5      | Block working at input TX clock | 60 |

|     | 5.5.1    | CLK_TX_GEN block                | 60 |

|     |          | LIST OF FIGURES                 |    |

| Fi  | onre 3.1 | .1-1 global description         | Q  |

| - 1 | 5010 2.1 | . 1 1 8100at accompanii         |    |

# SCOC

Ref :R&D-SOC-NT-292-V-ASTR

Issue : O rev. 2 Date : 18/06/2003

Page:5

| Figure 3.3.3-1 Storage format       | 15 |

|-------------------------------------|----|

| Figure 3.3.3-2 RX storage           | 16 |

| Figure 3.3.4-1 FIFO word format     | 18 |

| Figure 3.5.8-1 global architecture  | 32 |

| Figure 3.5.8-1 Reset trees          | 33 |

| Figure 3.7.2-1 TX shift registers   | 35 |

| Figure 3.7.6-1 RX clock generation  | 38 |

| Figure 3.8.1-1 RX shift registers   | 39 |

| Figure 3.9.7-1 FCT send function    | 45 |

| Figure 3.9.11-1 AHB_TX_INT FSM      | 50 |

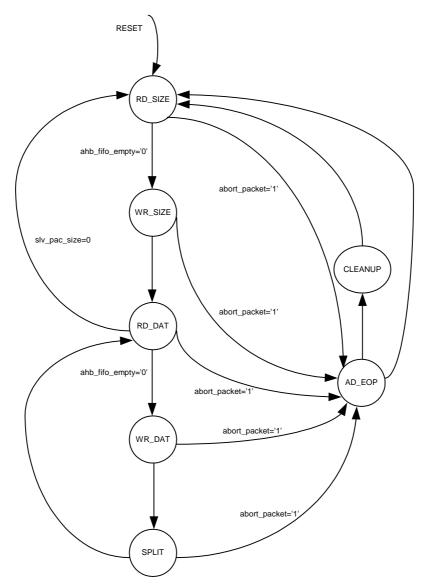

| Figure 3.9.12-1 TX Host Interface   | 52 |

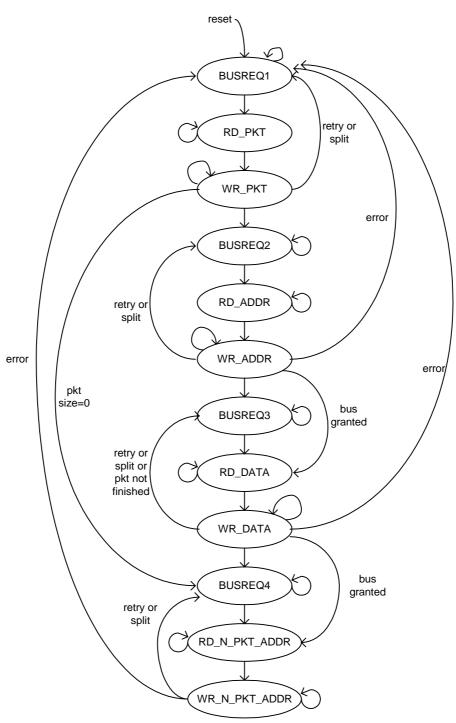

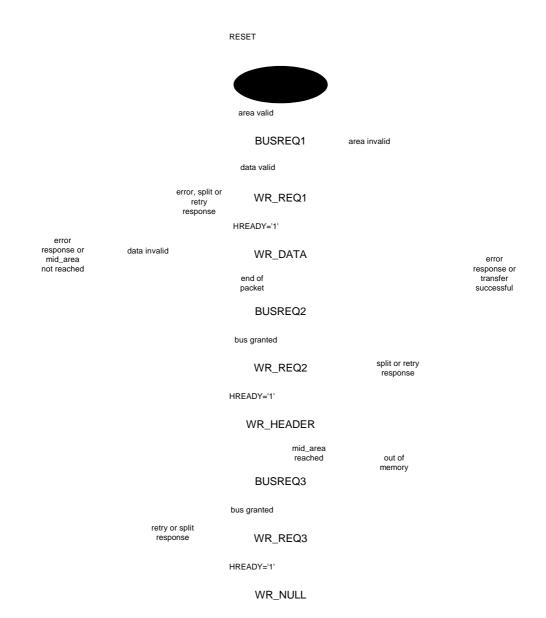

| Figure 3.9.12-2 AHB master FSM      | 53 |

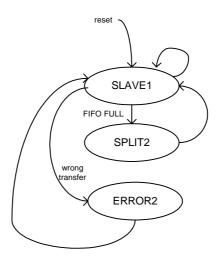

| Figure 3.9.12-3 AHB slave FSM       | 55 |

| Figure 3.9.13-1 RX Host Interface   | 56 |

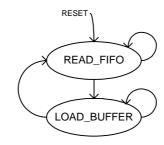

| Figure 3.9.13-2 Concatenation FSM   | 57 |

| Figure 3.9.13-3 RX AHB master FSM   | 58 |

| Figure 3.10.1-1 TX clock generation | 60 |

|                                     |    |

| LIST OF TABLES                      |    |

| Tableau 3.3.2-1 linked list element | 12 |

| Tableau 3.3.3-1 Packet format       | 14 |

| Tableau 3.3.4-1 Word meaning        | 18 |

| Tableau 3.9.1-1 State signification | 42 |

SCOC

Ref :R&D-SOC-NT-292-V-ASTR

Issue : O rev. 2 Date : 18/06/2003

Page: 6

PAGE INTENTIONALLY LEFT BLANK

Ref :R&D-SOC-NT-292-V-ASTR

Issue : O rev. 2 Date : 18/06/2003

Page : 7

#### 1 SCOPE

The present document is written in the frame of the ESA 13345/#3 contract "Building block for System on a Chip". It is part of Phase 3 of the contract related to the design of a System On a Chip for Space application. The present activity concerns the design of a Spacewire VHDL core to be integrated in the System On a CHip.

The present document describes the SpaceWire block developed as part of the ScoC project. This document contains the specification and the architecture of the block. The SpaceWire is a serial high speed link compliant with the ECSS-E-50-12 Draft 1 specification (AD11) delivered by ESA. For the SCoC project, the SpaceWire block (SWB) also contains AHB and APB interfaces.

### SCOC

Ref :R&D-SOC-NT-292-V-ASTR

Issue : O rev. 2 Date : 18/06/2003

Page:8

#### 2 DOCUMENTS AND ACRONYMS

#### 2.1 APPLICABLE DOCUMENTS

AD8 SCOC Requirement Specification R&D-RP-SOC-214-MMV, Issue 2,

June 2000

AD9 AMBA<sup>TM</sup> Specification Rev 2.0, ARM IHI 0011A

AD10 Spacecraft Controller On a Chip Architectural Design Document Draft

AD11 ECSS-E-50-12 Draft 1 (ESA SpaceWire Specification) March 2001

#### 2.2 REFERENCE DOCUMENTS

RD21 System-On-a-Chip Feasibility Study December 99, Issue 2, R&D-RP-

SOC-154-MMV

RD22 Spacewire IP Core Hardware User Manual December 2001, Issue 0, R&D-

SOC-NT-295-V-ASTR

#### 2.3 ACRONYMS

AD Applicable Document

APB Advanced Peripheral Bus

AHB Advanced High-Performance Bus

DMA Direct Memory Access

ESA European Space Agency

ESTEC European Space Research and Technology Centre

FPGA Field Programmable Gate Array

FSM Finite State Machine HKPF Housekeeping Function

HKAPB Housekeeping Advanced Peripheral Bus

IEEE Institute of Electrical and Electronics Engineers

IT Interrupt

LVDS Low Voltage Differential Signals SCoC Spacecraft Controller on a Chip

SWB SpaceWire Block

RD Reference Document

RHI RX Host Interface

SOC System-On-a-Chip

THI TX Host Interface

Ref :R&D-SOC-NT-292-V-ASTR

Issue : O rev. 2 Date : 18/06/2003

Page:9

#### 3 FUNCTIONAL DESCRIPTION

#### 3.1 GLOBAL FUNCTIONALITY DESCRIPTION

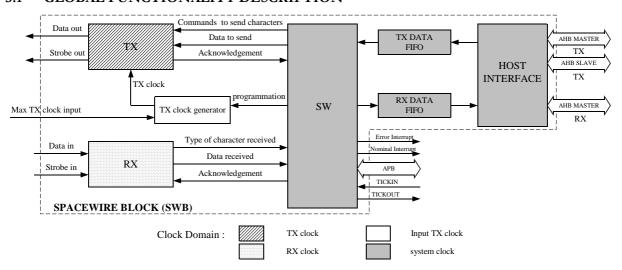

Figure 3.1.1-1 global description

The SWB is a high-speed serial link to transmit and receive packets of data (refer to AD11).

#### 3.1.1 Description of the different blocks

The Host Interface block is an interface with the AMBA AHB and APB buses. It contains the management of the data sent by the host. It manages the storage of data into the host memory.

The TX Data FIFO block is a FIFO containing the data to be transmitted.

The RX Data FIFO block is a FIFO containing the data to be stored into the host memory.

The SW block manages the initialisation protocol. This block selects the character to be transmitted and checks any error occurrence.

The TX block sends the character at the transmission frequency.

The RX block identifies the received character type.

The TX clock generator block generates the clock transmission rate.

#### 3.1.2 Introduction of the interfaces

The basic interface contains clock, test and resetn signals.

The APB interface is used to configure the SWB and to retrieve statuses.

The TX AHB master interface performs the TX DMA.

The TX AHB slave interface is used when the data transmission is in charge of the host.

The RX AHB master interface performs the storage of received data into the host memory.

The link interface brings together the data and strobe signals of the transmission and the reception.

Ref :R&D-SOC-NT-292-V-ASTR

Issue : O rev. 2 Date : 18/06/2003

Page : 10

The Time interface manages the transmission and the reception of time code.

The Interrupt interface is used to warn the host when a specific event appears.

#### 3.1.3 Link initialization

Refer to AD11 chapter 8.7.

#### 3.1.4 Transmission function

The SWB receives packets of data from the host through the AHB interface. Two modes are possible for this data transfer. The first one is the AHB master mode, which performs the transfer with a DMA mechanism. With the descriptor of a linked list of packets given by the host, the SWB retrieves 32-bit data of each packet of the linked list. The second one is the AHB slave mode. In this mode, the host transfers the length of the packet and the 32-bit data of the packet to the SWB.

Then the 32-bit data received from the host is split to 9-bit data to be stored into the TX data FIFO. The 9-bit data is composed of 8 bits of real data and 1 bit for particular character such as EOP and EEP (refer to AD11).

When the credit counter is positive (refer to AD11), the SW module fetches the 9-bit data in the TX data FIFO and sends it to the TX module with the right command to transmit this data. When the RX data FIFO free space allows the reception of 8 more bytes, the SW module generates an order to transmit a FCT. To transmit a time code, the TICKIN signal is activated so that the SW module generates the right transfer.

When the TX module receives a command from the SW module, an acknowledgement is generated. Then the character corresponding to the command is transmitted through the LVDS link (Data and Strobe outputs). The TX module automatically transmits NULL characters (refer to AD11) when no other transmission is requested.

The transmission frequency is programmable through the APB interface. The TX clock generator creates the required TX frequency, which can be **up to 4 times** the system clock frequency.

#### 3.1.5 Reception function

The RX module performs the recognition of the received character type. The RX clock is built from the data and strobe input signals (refer to AD11). The RX module also indicates the received characters to the SW module.

Each time that information of character type is received from the RX module, the SW module generates an acknowledgement. Then, following the received character, the SW module manages the credit counter and the outstanding counter. A 9-bit word is stored into the RX data FIFO when a data is received. The SW module also activates the TICKOUT signal when a right time code is received.

When the RX data FIFO is not empty, the host interface fetches its 9-bit data. Each time four 9-bit data are available, the host interface produces a 32-bit word from these four 9-bit data and stores it into the host memory through the AHB bus (master mode).

Ref :R&D-SOC-NT-292-V-ASTR

Issue : O rev. 2 Date : 18/06/2003

Page : 11

When any error is detected from the AHB transfer or from the transmission link, the SWB generates an error interrupt to warn the host. The SWB also produces a nominal interrupt to improve the monitoring.

The configuration of the SWB is done through the APB interface.

#### 3.2 FUNCTIONAL MODE DESCRIPTION

Refer to the state diagram of AD11 chapter 8.5.

The SWB supports the following functional modes:

- RESET mode (resetn=0):

- o TX and RX blocks are inactive

- Host interface is inactive

- ACTIVE mode (resetn=1):

- o TX block is inactive and RX block is active (when entering the ACTIVE mode)

- o Host interface is always on

The transition of the TX and RX states in the active mode is specified by the link initialisation protocol described in AD11.

Ref :R&D-SOC-NT-292-V-ASTR

Issue : O rev. 2 Date : 18/06/2003

Page: 12

#### 3.3 DETAILED FUNCTIONALITY DESCRIPTION

#### 3.3.1 TX clock programming

The FREQ\_INIT register configures the frequency in the initialisation state.

The FREQ\_RUN register configures the frequency in the run state.

For the gated TX clock configuration (see 5.2.1), when the TX\_MAX\_EN bit is asserted, the FREQ\_RUN register value is not taken into account and the transmission frequency is equal to the input TX clock frequency.

It is recommended not to change the FREQ\_INIT and FREQ\_RUN registers values when the spacewire link is in the RUN state.

See the internal register description paragraph for details.

#### 3.3.2 TX Host Interface (THI)

For the TX function, the SWB has 2 AHB interfaces:

- The master interface allows DMA transfer from the memory (or any other slave on the AHB bus) to the SpaceWire.

- The slave interface allows direct writing of data by an AHB master to the TX.

These interfaces are exclusive and the selection of the active interface is performed through the APB.

#### 3.3.2.1 TX DMA mode

When the SpaceWire is in the TX DMA mode, the host is able to transmit a linked list of packets. The format for an element of the linked list is depicted hereafter:

| Size of the packet (16 least significant bits, in bytes) |  |

|----------------------------------------------------------|--|

| Address of the first packet data (word aligned)          |  |

| Address of next linked list element (word aligned)       |  |

#### Tableau 3.3.2-1 linked list element

Writing the address of the descriptor list in a configuration register through the APB slave launches the DMA transfer. By knowing the size of the first packet by reading at this address, the SWB can reach the first data of the packet by reading at next address. With the size of the packet and the address of the first data, the SWB can fetch all the data of the packet. The SpaceWire can perform the same task for the next packet of the linked list. To end the linked list, the last element has a null value in its third field.

The THI makes single transfer on the AMBA AHB to retrieve the 32-bit data from the host.

For the last retrieved data corresponding to the current packet, the THI is able know the number of its valid bytes (this number depends on the packet size). In detail, considering that the data retrieved is

### SCOC

Ref :R&D-SOC-NT-292-V-ASTR

Issue : O rev. 2 Date : 18/06/2003

Page: 13

DAT(31:0), if 1 byte is valid, it will be DAT(31:24), if 2 bytes are valid, they will be DAT(31:24) and DAT(23:16) and so on...

The SWB inserts the End Of Packet (EOP) control character at the end of each packet.

If the retrieved packet size is null, the THI will skip the data retrieval process and looks for the next packet in the list.

The THI fetches and deliver all the data rapidly enough to keep the maximum data transfer rate (i.e. avoiding NULL character insertion: NULL character insertion must not be a consequence of the THI management of the AHB).

The TX DMA mode is only effective when the packet contains a big number of bytes.

In the worst case, the packet only contains 1 data byte. In this case, the THI has to perform 4 AHB accesses to fetch the data byte (1 access for the packet size, 1 access for the data address, 1 access for the data and 1 access for the next linked list element). Only 1 out of 4 accesses is used to retrieve the data, so NULL character insertion is inevitable. So for small packets, the host should use the TX slave mode to be effective.

If TX slave access is performed during TX DMA mode, the TX slave block will activate the WRONG\_MODE interrupt and an AHB error response is delivered.

The host can monitor the progression in the linked list of packets by reading the descriptor register.

The transfer is aborted by asserting the ABORT\_PACKET bit. The THI adds an EEP into the TX FIFO and erases the current data received from the host. The host should launch a new TX DMA only after the ABORT\_PACKET auto-reset i.e. after the end of the abortion process.

If the THI receives an AHB error response, the TX DMA will stop retrieving data.

To restart the TX DMA after an AHB error reception, the host activates the ABORT\_PACKET bit of the management register in order to properly end the current packet transmission. After the autoreset of the ABORT\_PACKET bit, the host can launch the TX DMA again.

#### 3.3.2.2 TX slave mode

The TX AHB slave interface doesn't take care of the input addresses.

After reset, the first 32-bit data sent by the host to the THI is the 16-bit size of the packet it wants to transfer (only the 16 least significant bits of the data are taken into account). The size is in bytes. If the THI receives a null packet size, it will not take it into account and will expect to receive another packet size.

Then the host can deliver the data corresponding to this packet. The SWB considers the received data as belonging to the current packet as long as the corresponding byte number does not reach the packet size. Each 32-bit data contains 4 valid bytes, the last 32-bit data contains at least 1 valid byte. Each byte is stored into the TX FIFO.

When the packet size is reached, the THI adds an EOP into the TX FIFO and expects to receive the size of the next packet.

The TX slave is able to accept burst transfer.

### SCOC

Ref :R&D-SOC-NT-292-V-ASTR

Issue : O rev. 2 Date : 18/06/2003

Page : 14

The host can stop the current packet transfer by asserting the ABORT\_PACKET bit. When this bit is asserted, the THI adds an EEP into the TX FIFO and erases the current received data. The host should access to the TX slave only after the ABORT\_PACKET auto-reset i.e. after the end of the abortion process. The next data received from the host is regarded as the size of the next packet to transmit.

When the TX FIFO is full, the THI will generate a split response (AMBA protocol) to the host if a new data transfer is requested. If a split response has been generated and another request (from the same master) is received before the transfer completion, the THI will give another split response.

When the THI receives a request from a master but cannot handle the request, it gives a split response. Before the transfer completion, if another master (different from the first one) requests the THI, the THI will response with an error message.

If the THI receives a request from a master while the link is not connected, the THI will send an error response. Then, a specific interrupt will be generated. If the split has been activated, it will be released.

Only one master should dialogue with the THI to avoid any confusion of data.

#### 3.3.3 RX Host Interface (RHI)

#### 3.3.3.1 The format of the storage

For the RX, the SpaceWire IP has one AHB interface. This interface allows DMA transfers from the RX FIFO to an AHB slave. The RX interface transfers data in packet format to the AHB slave. The format of a packet is described hereafter:

| Header (32 bits) |

|------------------|

| Data (32 bits)   |

| Data (32 bits)   |

|                  |

Tableau 3.3.3-1 Packet format

#### Header contents:

- bit 31 down to 18: unused

- bit 17 down to 16: status

- bit 15 down to 0 : packet size

The 2-bit status indicates the validity of the current packet (complete packet or incomplete packet because of link error, EEP reception or no space left in memory area). The packet size indicates the number of bytes of the packet.

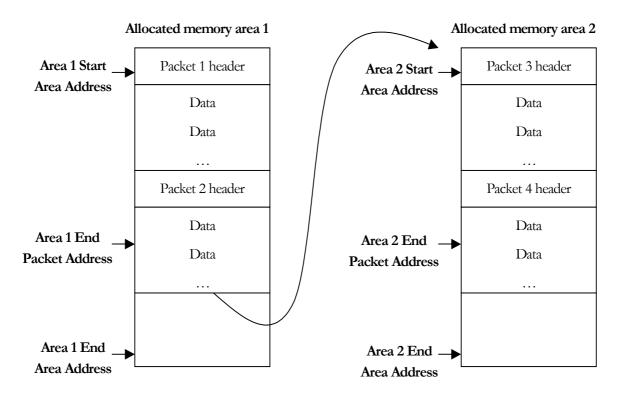

The host allocates two memory areas (1 and 2) and configures 2 sets (one for each area) of three word aligned addresses in the SWB. The first address, called Start\_Area Address, represents the beginning of (1 or 2) allocated area, the second address, called End\_Packet Address, is close to the (1 or 2) allocated area end and the last address, called End\_Area Address, is the real end of the (1 or 2) allocated area.

### SCOC

Ref :R&D-SOC-NT-292-V-ASTR

Issue : O rev. 2 Date : 18/06/2003

Page : 15

The couple of three addresses is written in the SpaceWire Configuration registers through the APB bus by the CPU. In addition to these addresses, the host provides a command indicating the validity of the areas.

Practically, the host validates one memory area at least to enable the Rx data transfer from the Rx FIFO to the host memory. For this, the Start\_Area, End\_Packet and End\_Area Registers is programmed and the AREA1\_VALID or/and AREA2\_VALID bit(s) is set to validate the memory area(s).

The following figure shows the host memory allocation.

Figure 3.3.3-1 Storage format

### SCOC

Ref :R&D-SOC-NT-292-V-ASTR

Issue : O rev. 2 Date : 18/06/2003

Page : 16

#### 3.3.3.2 The functionality of the RHI

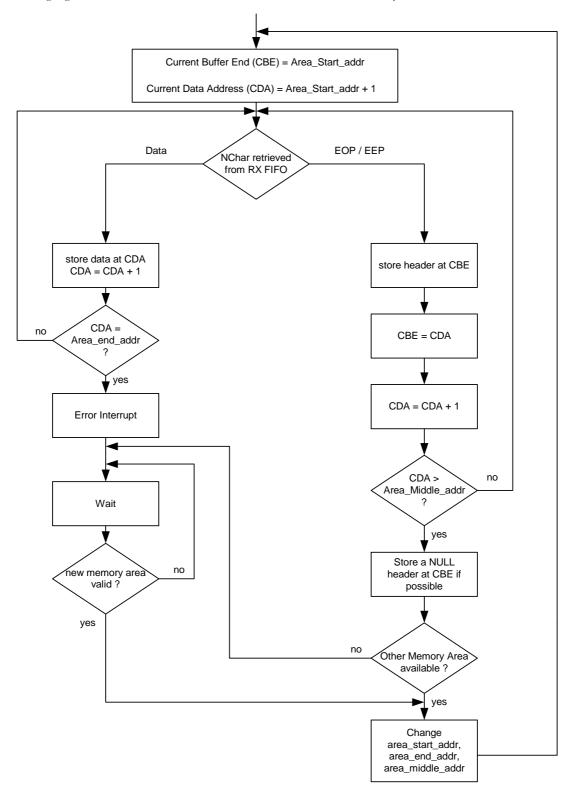

The following figure shows how the RHI stores data into the host memory.

Figure 3.3.3-2 RX storage

SCOC

Ref :R&D-SOC-NT-292-V-ASTR

Issue : O rev. 2 Date : 18/06/2003

Page: 17

The RHI indicates the current end of the currently used area (1 or 2), called Current Buffer End. When the area is empty, the Current Buffer End is the Start Address of this area. When an entire packet is stored into the used area, the Current Buffer End indicates the address of the next packet header. The EOP or EEP is not written into the host memory. Depending on the packet size, the last data of the packet may contain 1, 2, 3 or 4 valid bytes. The rule to determine which ones are valid is the same as in TX Host Interface. The Current Buffer End is only updated when the entire current packet is stored.

The RHI indicates the used memory area (AREA1\_USED or AREA2\_USED bit in the management register) so that the host can follow the storage progression by monitoring the Current Buffer End.

The RHI uses the Start Address to start writing packets in host memory in a given area (1 or 2). The RHI first attempts to use area 1. During packet data reception and up to the reception of the end of packet, the RHI leaves the packet header empty. When an end of packet is detected in the Rx FIFO, the RHI fills the header of the packet that it had just finished to write. The status will be set to "01" if an EEP has been retrieved from the Rx FIFO, it will be set to "10" if there is no space left in the memory area to complete the packet transfer, otherwise the status bit will be "00". The packet size is filled with the number of bytes of the packet.

In case the RX receives data and no area is allocated, the SWB generates the NO\_AREA\_VALID interrupt.

If the SWB receives a NULL character and the link is not enabled, the LINK\_NOT\_ENABLED interrupt will be generated to warn the host.

#### 3.3.3.3 Reaching the End\_Packet Address

If the RHI reaches the End\_Packet Address during a packet transfer, it will write a null header into the current memory area after the last data of the current packet. If no space is available, the null header will not be written. Then the current AREA1\_USED or AREA2\_USED bit is reset. The SWB then invalidates the current memory area by resetting the AREA1\_VALID or AREA2\_VALID bit. The revalidation of the area or the definition of a new area is in charge of the host.

If the other allocated area is valid, the RHI will continue transferring the next packet into the other available allocated area. If the other area is not valid, the RHI will generate the NO\_AREA\_VALID interrupt and stops the packet transfer until the host provides another available area.

#### 3.3.3.4 Reaching the End\_Area Address

If the RHI reaches the End\_Area Address before ending writing the current packet, the RHI will write the packet header with the current number of bytes written in the buffer as packet size and with the status "10" indicating that the packet contains no error but is incomplete. The status "10" will be generated even if all the packet data are written.

The EXCEED\_MEM interrupt is activated.

The remaining data of the packet is written in another available memory area and is considered as an entire packet. So it is the host responsibility to concatenate the beginning of the packet with the end of the packet (the packet can be split between areas 1 and 2) or to perform any other recovery actions (link restart,...).

Ref :R&D-SOC-NT-292-V-ASTR

Issue : O rev. 2 Date : 18/06/2003

Page: 18

#### 3.3.3.5 AHB error occurrence

When the RHI receives an error response, the data storage stops without ending the current packet storage. Both memory areas become invalid.

The storage starts again when a memory area is validated. The last part of the incompletely stored packet is written into the new valid memory area.

#### 3.3.3.6 Advice

The space between the End Packet Address and the End Area Address should be at least equal to the maximal size of a packet (expected to be received by the host) in order to guarantee a safe protocol.

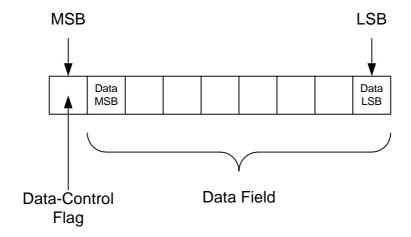

#### 3.3.4 Format of the words stored in the TX and RX FIFOs:

The TX and RX FIFOs contain 9-bit words.

Figure 3.3.4-1 FIFO word format

|         | Control flag | Data Bits(MSBLSB) | Meaning    |

|---------|--------------|-------------------|------------|

|         | 0            | XXXXXXXX          | 8-bit data |

| TX FIFO | 1            | XXXXXXX0          | ЕОР        |

|         | 1            | XXXXXXX1          | EEP        |

|         | 0            | XXXXXXXX          | 8-bit data |

| RX FIFO | 1            | 00000000          | ЕОР        |

|         | 1            | 00000001          | EEP        |

Tableau 3.3.4-1 Word meaning

See the AD11 for details.

#### 3.3.5 The interrupts

Ref :R&D-SOC-NT-292-V-ASTR

Issue : O rev. 2 Date : 18/06/2003

Page : 19

The Internal Register Description paragraph shows all the interrupts. An interrupt remains active until its reset.

When an interrupt is asserted, the host should perform all the corresponding tasks before clearing this interrupt by writing into the IT\_RESET register.

The ITMASKREG allows inhibiting the output interrupt signals (nominal interrupt and error interrupt) but doesn't inhibit the interrupt register. Interrupt register bits will still be set.

#### 3.3.6 Time Code transmission and reception

To send a time code, the host either generates a pulse on the TICKIN\_CTM input signal or asserts the TICKIN bit of the management register. A time code is sent when a rising edge is detected on TICKIN\_CTM or TICKIN.

It is possible to initialise the time code value by writing in the time code register (TIMESEND\_REG byte).

When a correct time code is received, the SWB generates a pulse on the TICKOUT\_CTM output signal and the TICKOUT interrupt is asserted.

The received time code value is in the time code register (TIMEREC\_REG byte).

#### 3.3.7 Test mode

The test mode is activated when TEST\_MODE\_HARD and TEST\_MODE\_SOFT are high.

The test mode allows invalidating the host memory areas. See the Internal Register Description paragraph.

Ref :R&D-SOC-NT-292-V-ASTR

Issue : O rev. 2 Date : 18/06/2003

Page: 20

#### 3.4 INTERNAL REGISTER DESCRIPTION

All the SWB registers are accessible through the APB interface. The input address is interpreted as a byte address, as per AD9. Since each access is a word access, the two least significant address bits are assumed always to be zero. Only address bits 6:2 are decoded. Misaligned addressing is not supported. For read accesses, data output is produced combinatorially from the address.

#### 3.4.1 Global description

| Register name              | Address (Hex) | Read/Write | Remark                                      | Reference  |

|----------------------------|---------------|------------|---------------------------------------------|------------|

| Management                 | 00            | r/w        | link management and status.                 | Tableau 2  |

| Interrupt                  | 04            | r          | Interrupt status.                           | Tableau 3  |

| Current Buffer End         | 08            | r          | Current end of the used memory area.        | Tableau 4  |

| Start Address 1            | 0C            | r/w        | Memory area 1 start address                 | Tableau 5  |

| Start Address 2            | 10            | r/w        | Memory area 2 start address                 | Tableau 6  |

| Middle Address 1           | 14            | r/w        | Memory area 1 packet end                    | Tableau 7  |

| Middle Address 2           | 18            | r/w        | Memory area 2 packet end                    | Tableau 8  |

| End Address 1              | 1C            | r/w        | Memory area 1 end address                   | Tableau 9  |

| End Address 2              | 20            | r/w        | Memory area 2 end address                   | Tableau 10 |

| Descriptor                 | 24            | r/w        | First address of the linked list of packets | Tableau 11 |

| Time Out                   | 28            | r/w        | Time out programmation                      | Tableau 12 |

| Interrupt Mask             | 2C            | r/w        |                                             | Tableau 13 |

| Interrupt reset            | 30            | W          |                                             | Tableau 14 |

| Interrupt set              | 34            | W          |                                             | Tableau 15 |

| Time Code                  | 38            | r/w        | Time code programmation and status          | Tableau 16 |

| Additional status register | 3C            | r          |                                             | Tableau 17 |

## SCOC

Ref :R&D-SOC-NT-292-V-ASTR

Issue : O rev. 2 Date : 18/06/2003

Page: 21

### 3.4.2 Detailed description

Management Register: address 00H

| Bits  | Name          | Reset<br>Value | Function                                                                                                                                                                                                                                                                                                                              | r/w |

|-------|---------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 31-24 | FREQ_INIT     | 0              | Configuration of the TX clock frequency used during the link initialisation. See 5.2.1.  In the gated TX clock configuration, the input TX clock frequency is divided by 2(FREQ_INIT+1) then is used as TX frequency.  In the not-gated TX clock configuration, the input TX clock frequency is divided by (FREQ_RUN+1).              |     |

| 23-16 | FREQ_RUN      | 0              | Configuration of the TX clock frequency used after the link initialisation. See 5.2.1.  In the gated TX clock configuration, the input TX clock frequency is divided by 2(FREQ_RUN+1) then is used as TX frequency if TX_MAX_EN=0.  In the not-gated TX clock configuration, the input TX clock frequency is divided by (FREQ_RUN+1). |     |

| 15-13 | ST_TRANS      | 0              | Status showing the link initialisation progression.  0 to 4: initialisation state (0=ErrorReset, 1=ErrorWait, 2=Ready, 3=Started, 4=Connecting)  5: run state                                                                                                                                                                         | r   |

| 12    | TICKIN        | 0              | The host can transmit a time code by asserting this bit. Writing a '1' launches the time code transmission Writing a '0' has no effect                                                                                                                                                                                                | W   |

| 11    | LINK_DISABLED | 0              | The link is disabled.  0: link not disabled  1: link disabled                                                                                                                                                                                                                                                                         | r/w |

| 10    | LINK_START    | 0              | The link can start.  0: link not started  1: link started                                                                                                                                                                                                                                                                             | r/w |

| 9     | AUTOSTART     | 0              | The link automatically starts when a NULL character is received.  0: autostart off 1: autostart on                                                                                                                                                                                                                                    | r/w |

| 8     | TX_MAX_EN     | 0              | This bit is only used with the gated TX clock configuration. In run state, the TX frequency used will be the same as the input TX clock frequency if this bit is                                                                                                                                                                      |     |

## SCOC

Ref :R&D-SOC-NT-292-V-ASTR

Issue : O rev. 2 Date : 18/06/2003

Page : 22

| Bits N | ame            | Reset<br>Value | Function                                                     | r/w |

|--------|----------------|----------------|--------------------------------------------------------------|-----|

|        |                |                | asserted. See 5.2.1.                                         |     |

|        |                |                | 0: max TX frequency Off                                      |     |

|        |                |                | 1: max TX frequency On                                       |     |

| 7      | DMA_RUNNING    | 0              | This bit indicates if the DMA is running or not.             |     |

|        |                |                | 0: DMA is not running                                        |     |

|        |                |                | 1: DMA is running                                            |     |

| 6      | AHB_MODE_TX    | 0              | The host has 2 possibilities to transfer data to the SWB.    | r/w |

|        |                |                | 0: TX AHB slave                                              |     |

|        |                |                | 1: TX AHB master (DMA)                                       |     |

| 5      | TEST_MODE_SOFT | 0              | When TEST_MODE_HARD input signal and                         | r/w |

|        |                |                | TEST_MODE_SOFT are asserted, the test mode is active.        |     |

| 4      | ABORT_PACKET   | 0              | Abortion of the data transfers. Writing a '1' launches the   | r/w |

|        |                |                | abortion process.                                            |     |

|        |                |                | Writing a '0' has no effect.                                 |     |

|        |                |                | This bit is automatically reset when the abortion process    |     |

|        |                |                | ends.                                                        |     |

| 3      | AREA2_USED     | 0              | This bit is asserted when the host memory area 2 is used to  | r   |

|        |                |                | store the data from the SWB.                                 |     |

| 2      | AREA1_USED     | 0              | This bit is asserted when the host memory area 1 is used to  | r   |

|        |                |                | store the data from the SWB.                                 |     |

| 1      | AREA2_VALID    | 0              | This bit validates the area 2. So the SWB can use the area 2 | r/w |

|        |                |                | to store data.                                               |     |

|        |                |                | Writing a '1' validates the area 2.                          |     |

|        |                |                | Writing a '0' has no effect.                                 |     |

|        |                |                | This bit is automatically reset when the area 2 is full.     |     |

|        |                |                | In test mode, writing a '0' will reset this bit.             |     |

| 0      | AREA1_VALID    | 0              | This bit validates the area 1. So the SWB can use the area 1 | r/w |

|        |                |                | to store data.                                               |     |

|        |                |                | Writing a '1' validates the area 1.                          |     |

|        |                |                | Writing a '0' has no effect.                                 |     |

|        |                |                | This bit is automatically reset when the area 1 is full.     |     |

|        |                |                | In test mode, writing a '0' will reset this bit.             |     |

#### Tableau 2

<u>Warning 1</u>: To let unchanged the validity of the AREA1 and AREA2, the user must write '0' in bit 0 and bit 1 each time a write access is performed in this register.

<u>Warning 2</u>: To prevent accidental transfer abortion, the user must write '0' in bit 4 each time a write access is performed in this register.

# SCOC

Ref :R&D-SOC-NT-292-V-ASTR

Issue : O rev. 2 Date : 18/06/2003

Page: 23

#### Interrupt Register: address 04H

| Bits | Name             | Reset<br>Value | Function                                                                                                                                                                        | r/w |

|------|------------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 16   | PACKET_REC       | 0              | This bit is asserted when a complete packet has been received.  Nominal Interrupt                                                                                               | r   |

| 15   | LINK NOT ENABLED | 0              | This bit is asserted when a NULL character is received but the link is not enabled (LINK_DISABLED On or LINK_START Off and AUTOSTART Off)  Nominal Interrupt                    |     |

| 14   | EXCEED_MEM       | 0              | When the SWB cannot store a packet entirely because the host memory area is full, this bit is asserted.  Nominal Interrupt                                                      | r   |

| 13   | TICKOUT          | 0              | This bit is asserted when a right time code has been received.  Nominal Interrupt                                                                                               | r   |

| 12   | END_LIST         | 0              | In TX AHB master mode, when the SWB reaches the end of the linked list of packets, this bit is asserted.  Nominal Interrupt                                                     | r   |

| 11   | NO_AREA_VALID    | 0              | When data have been received but any host memory area is available, this bit is asserted.  Nominal Interrupt                                                                    | r   |

| 10   | WRONG_MODE       | 0              | Writing in the descriptor register (24H) while in TX AHB slave mode or writing in the TX AHB slave while in TX AHB master mode will assert the WRONG_MODE bit.  Error Interrupt | r   |

| 9    | RD_ACCESS_ERROR  | 0              | A read access to the TX AHB slave will assert this bit. A AHB error response will be generated.  Error Interrupt                                                                | r   |

| 8    | AMBA_ERROR       | 0              | This bit is asserted when the SWB receives a AHB error response.  Error Interrupt                                                                                               | r   |

| 7    | LINK_NOT_READY   | 0              | This bit is asserted when the TX AHB slave is selected and the link is not connected.  Error Interrupt                                                                          |     |

| 6    | EEP_REC          | 0              | This bit is asserted when a EEP has been received.  Error Interrupt                                                                                                             | r   |

| 5    | CREDIT_ERR       | 0              | This bit is asserted when the SWB receives a FCT but the increment of the credit counter will exceed 56.  Error Interrupt                                                       | r   |

| 4    | OUTSTAND_ERR     | 0              | This bit is asserted when the SWB receives a data but is not waiting for any one (outstanding counter at 0).                                                                    | r   |

## SCOC

Ref :R&D-SOC-NT-292-V-ASTR

Issue : O rev. 2 Date : 18/06/2003

Page: 24

| Bits N | ame            | Reset | Function                                                    | r/w |

|--------|----------------|-------|-------------------------------------------------------------|-----|

|        |                | Value |                                                             |     |

|        |                |       | Error Interrupt                                             |     |

| 3      | CHAR_SEQ_ERR   | 0     | This bit is asserted when a character sequence error is     | r   |

|        |                |       | detected.                                                   |     |

|        |                |       | Error Interrupt                                             |     |

| 2      | DISCONNECT_ERR | 0     | This bit is asserted when a link disconnection is detected. | r   |

|        |                |       | Error Interrupt                                             |     |

| 1      | PARITY_ERR     | 0     | This bit is asserted when a parity error is detected.       | r   |

|        |                |       | Error Interrupt                                             |     |

| 0      | ESC_ERR        | 0     | This bit is asserted when a received ESC character is       | r   |

|        |                |       | followed by neither a FCT nor a data.                       |     |

|        |                |       | Error Interrupt                                             |     |

#### Tableau 3

The active value of an interrupt is '1'.

#### Current Buffer End Register: address 08H

| Bits | Name        | Reset<br>Value | Function                                                                                                                                                                                                          | r/w |

|------|-------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 31-0 | CUR_BUF_END | 0              | This address pointer indicates the current end of the used host memory area. All addresses between the start address value and the address pointer value (address pointer value not included) contain valid data. |     |

#### Tableau 4

#### Start Address 1 Register: address 0CH (see note 1)

| Bits | Name        | Reset<br>Value | Function                                                     | r/w |

|------|-------------|----------------|--------------------------------------------------------------|-----|

| 31-0 | START_AREA1 | 0              | This address pointer indicates the start address of the host | r/w |

|      |             |                | memory area 1.                                               |     |

#### Tableau 5

#### Start Address 2 Register: address 10H (see note 1)

| Bits | Name        | Reset<br>Value | Function                                                                    | r/w |

|------|-------------|----------------|-----------------------------------------------------------------------------|-----|

| 31-0 | START_AREA2 | 0              | This address pointer indicates the start address of the host memory area 2. | r/w |

#### Tableau 6

Middle Address 1 Register: address 14H (see note 1)

Ref :R&D-SOC-NT-292-V-ASTR

Issue : O rev. 2 Date : 18/06/2003

Page: 25

| Bits | Name     | Reset<br>Value | Function                                                      | r/w |

|------|----------|----------------|---------------------------------------------------------------|-----|

| 31-0 | END_PAC1 | 0              | This address pointer indicates the middle address of the host | r/w |

|      |          |                | memory area 1.                                                |     |

#### Tableau 7

#### Middle Address 2 Register: address 18H (see note 1)

| Bits | Name     | Reset<br>Value | Function                                                                     | r/w |

|------|----------|----------------|------------------------------------------------------------------------------|-----|

| 31-0 | END_PAC2 | 0              | This address pointer indicates the middle address of the host memory area 2. | r/w |

#### Tableau 8

#### End Address 1 Register: address 1CH (see note 1)

| Bits | Name      | Reset<br>Value | Function                                                   | r/w |

|------|-----------|----------------|------------------------------------------------------------|-----|

| 31-0 | END_AREA1 | 0              | This address pointer indicates the end address of the host | r/w |

|      |           |                | memory area 1.                                             |     |

#### Tableau 9

#### End Address 2 Register: address 20H (see note 1)

| Bits | Name      | Reset<br>Value | Function                                                                  | r/w |

|------|-----------|----------------|---------------------------------------------------------------------------|-----|

| 31-0 | END_AREA2 | 0              | This address pointer indicates the end address of the host memory area 2. | r/w |

#### Tableau 10

#### Descriptor Register: address 24H

| Bits | Name      | Reset<br>Value | Function                                                        | r/w |

|------|-----------|----------------|-----------------------------------------------------------------|-----|

| 31-0 | DESC_ADDR | 0              | By writing in this register, the host gives the first element   |     |

|      |           |                | address of the linked list of packets. For a nominal operation, |     |

|      |           |                | the host must not write again in this register before the       |     |

|      |           |                | END_LIST interrupt activation.                                  |     |

|      |           |                | By reading in this register, the host can monitor the           |     |

|      |           |                | progression in the linked list.                                 |     |

#### Tableau 11

## SCOC

Ref :R&D-SOC-NT-292-V-ASTR

Issue : O rev. 2 Date : 18/06/2003

Page: 26

#### Time-Out Register: address 28H (see note 2)

| Bits  | Name        | Reset | Function                                                      | r/w |

|-------|-------------|-------|---------------------------------------------------------------|-----|

|       |             | Value |                                                               |     |

| 23-16 | DIS_CNT_LIM | FF    | This is the time out for the link disconnection detection.    | r/w |

|       |             |       | DIS_CNT_LIM = 1 means time out = 1 system clock period        |     |

|       |             |       | The DIS_CNT_LIM will take a definite value so that the        |     |

|       |             |       | time-out is set to 850 ns.                                    |     |

| 15-8  | RESERVED    |       | Not used for the moment. These bits will be used if the       |     |

|       |             |       | DELAYWIDTH constant becomes higher than 8 (Refer to           |     |

|       |             |       | RD22)                                                         |     |

| 7-0   | DELAY_6_4   | FF    | This is the 6.4 µs time out used in the link initialization   | r/w |

|       |             |       | protocol. The user will give a value so that this time out is |     |

|       |             |       | about 6.4 μs.                                                 |     |

|       |             |       | DELAY_6_4 = 1 means time out = 1 system clock period          |     |

#### Tableau 12

#### Interrupt Mask Register: address 2CH

| Bits | Name      | Reset<br>Value | Function                                              | r/w |

|------|-----------|----------------|-------------------------------------------------------|-----|

| 15-0 | ITMASKREG | 1              | This register masks the interrupts.                   | r/w |

|      |           |                | bit at '0': the corresponding interrupt is masked     |     |

|      |           |                | bit at '1': the corresponding interrupt is not masked |     |

#### Tableau 13

#### Interrupt Reset: address 30H

| Bits | Name     | Reset<br>Value | Function                                                      | r/w |

|------|----------|----------------|---------------------------------------------------------------|-----|

| 15-0 | IT_RESET | -              | The host can reset the interrupts by writing at this address. | w   |

|      |          |                | Writing a '0': the corresponding interrupt is reset           |     |

|      |          |                | Writing a '1': no effect on the corresponding interrupt       |     |

#### Tableau 14

#### Interrupt Set: address 34H

| Bits | Name   | Reset<br>Value | Function                                                    | r/w |

|------|--------|----------------|-------------------------------------------------------------|-----|

|      |        | value          |                                                             |     |

| 15-0 | IT_SET | -              | The host can set the interrupts by writing at this address. | W   |

|      |        |                | Writing a '0': no effect on the corresponding interrupt     |     |

|      |        |                | Writing a '1': the corresponding interrupt is set           |     |

#### Tableau 15

## SCOC

Ref :R&D-SOC-NT-292-V-ASTR

Issue : O rev. 2 Date : 18/06/2003

Page: 27

#### Time Code Register: address 38H

| Bits | Name         | Reset<br>Value | Function                                             | r/w |

|------|--------------|----------------|------------------------------------------------------|-----|

| 15-8 | TIMESEND_REG | 0              | The host can initiate the time code value to send.   | r/w |

| 7-0  | TIMEREC_REG  | 0              | This register contains the received time code value. | r   |

#### Tableau 16

Note 1: For this register, the value must be an address aligned with a 32-bit data.

#### Additional Status Register: address 3CH

| Bits  | Name            | Reset<br>Value | Function                                                                                                        | r/w |

|-------|-----------------|----------------|-----------------------------------------------------------------------------------------------------------------|-----|

| 17    | FIFO_FULL       | 0              | In AHB slave mode, this flag indicates the state of the 32-bit AHB FIFO.  • 0: not full • 1: full               |     |

| 16    | GATED_TX_CLOCK  | -              | Indicates the TX clock configuration:  ➤ 0: Not-gated TX clock configuration  ➤ 1: Gated TX clock configuration |     |

| 15-14 | UNUSED          |                |                                                                                                                 |     |

| 13-8  | OUTSTANDING_CNT | 0              | Outstanding counter value.                                                                                      | r   |

| 7-6   | UNUSED          |                |                                                                                                                 |     |

| 5-0   | CREDIT_CNT      | 0              | Credit counter value.                                                                                           | r   |

Tableau 17

Ref :R&D-SOC-NT-292-V-ASTR

Issue : O rev. 2 Date : 18/06/2003

Page: 28

#### 3.5 INTERFACE DESCRIPTION

#### 3.5.1 Clocks, test and reset

| Signal name    | I/O | Description                                                             | Active value |

|----------------|-----|-------------------------------------------------------------------------|--------------|

| clk_txin       | Ι   | Max transmission clock. Lower TX frequency is a division of this clock. | -            |

| clk_sw         | Ι   | system clock                                                            | -            |

| test_mode_hard | Ι   | asynchronous signal to activate the test mode                           | 1            |

| resetn         | Ι   | asynchronous reset                                                      | 0            |

#### 3.5.2 APB interface

| Signal name                                                                       | I/O | Description                                             | Active value |

|-----------------------------------------------------------------------------------|-----|---------------------------------------------------------|--------------|

| apb_slv_in.PWDATA(31-0) apb_slv_in.PSEL apb_slv_in.PENABLE apb_slv_in.PADDR(31-0) | I   | AMBA APB bus in. (Sampled on the clk_sw rising edge)    | -            |

| apb_slv_out.PRDATA(31-0)                                                          | О   | AMBA APB bus out. (generated on the clk_sw rising edge) | -            |

#### 3.5.3 TX AHB master interface

| Signal name                | I/O | Description                              | Active |

|----------------------------|-----|------------------------------------------|--------|

|                            |     |                                          | value  |

| tx_ahb_mst_in.HGRANT       | Ι   | AMBA AHB master bus in for the TX        | -      |

| tx_ahb_mst_in.HREADY       |     | host interface. (Sampled on the clk_sw   |        |

| tx_ahb_mst_in.HRESP(1-0)   |     | rising edge)                             |        |

| tx_ahb_mst_in.HRDATA(31-0) |     |                                          |        |

| tx_ahb_mst_in.HCACHE       |     |                                          |        |

| tx_ahb_mst_out.HBUSREQ     | О   | AMBA AHB master bus out for the TX       | -      |

| tx_ahb_mst_out.HTRANS      |     | host interface. (generated on the clk_sw |        |

| tx_ahb_mst_out.HADDR(31-0) |     | rising edge)                             |        |

| tx_ahb_mst_out.HWRITE      |     |                                          |        |

# SCOC

Ref :R&D-SOC-NT-292-V-ASTR Issue : O rev. 2

Date : 18/06/2003 Page : 29

| tx_ahb_mst_out.HSIZE(2-0)   |  |  |

|-----------------------------|--|--|

| tx_ahb_mst_out.HBURST(2-0)  |  |  |

| tx_ahb_mst_out.HPROT(3-0)   |  |  |

| tx_ahb_mst_out.HWDATA(31-0) |  |  |

#### 3.5.4 TX AHB slave interface

| Signal name                                                                                                                                                                                                                                                                           | I/O | Description                                                                             | Active value |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----------------------------------------------------------------------------------------|--------------|

| tx_ahb_slv_in.HSEL  tx_ahb_slv_in.HWRITE  tx_ahb_slv_in.HADDR(31-0)  tx_ahb_slv_in.HTRANS(1-0)  tx_ahb_slv_in.HWDATA(31-0)  tx_ahb_slv_in.HREADY  tx_ahb_slv_in.HSIZE(2-0)  tx_ahb_slv_in.HMASTER(3-0)  tx_ahb_slv_in.HMASTLOCK  tx_ahb_slv_in.HBURST(2-0)  tx_ahb_slv_in.HBURST(2-0) | I   | AMBA AHB slave bus in for the TX host interface. (Sampled on the clk_sw rising edge)    | -            |

| tx_ahb_slv_out.HREADY tx_ahb_slv_out.HRESP(1-0) tx_ahb_slv_out.HRDATA(31-0) tx_ahb_slv_out.HSPLIT(15-0)                                                                                                                                                                               | O   | AMBA AHB slave bus out for the TX host interface. (generated on the clk_sw rising edge) | -            |

Ref :R&D-SOC-NT-292-V-ASTR

Issue : O rev. 2 Date : 18/06/2003

Page: 30

#### 3.5.5 RX AHB master interface

| Signal name    | I/O | Description                                                                              | Active value |

|----------------|-----|------------------------------------------------------------------------------------------|--------------|

| rx_ahb_mst_in  | Ι   | AMBA AHB master bus in for the RX host interface. (Sampled on the clk_sw rising edge)    | -            |

| rx_ahb_mst_out | О   | AMBA AHB master bus out for the RX host interface. (generated on the clk_sw rising edge) | -            |

#### 3.5.6 Link interface

| Signal name | I/O | Description                                                            | Active<br>value |

|-------------|-----|------------------------------------------------------------------------|-----------------|

| d_in        | Ι   | asynchronous input data signal                                         | -               |

| s_in        | Ι   | asynchronous input strobe signal                                       | -               |

| d_out       | О   | output data signal. (Generated on the internal TX clock rising edge)   | -               |

| s_out       | О   | output strobe signal. (Generated on the internal TX clock rising edge) | -               |

#### 3.5.7 Time interface

| Signal name | I/O | Description                                                     | Active<br>value |

|-------------|-----|-----------------------------------------------------------------|-----------------|

| tickin_ctm  | Ι   | signal to send time code. (Sampled on the clk_sw rising edge)   | 1               |

| tickout_ctm | О   | right time code received. (Generated on the clk_sw rising edge) | 1               |

#### 3.5.8 Interrupt interface

| Signal name | I/O | Description                                                   | Active<br>value |

|-------------|-----|---------------------------------------------------------------|-----------------|

| err_int     | О   | output error interrupt. (Generated on the clk_sw rising edge) | 1               |

| nom_int     | О   | output error interrupt. (Generated on the clk_sw rising edge) | 1               |

Ref :R&D-SOC-NT-292-V-ASTR

Issue : O rev. 2 Date : 18/06/2003

Page: 31

#### 4 PERFORMANCE

The TX frequency can be up to 4 times the system clock frequency.

The RX rate can be up to 4 times the system clock frequency.

The Time Code transmission order is taken into account 1 system clock period after its generation. But the real Time Code transmission depends on the length of the current transmitted character.

When data have to be transmitted, no Null character is transmitted between 2 data transmissions. But when the TX master mode is used and the packet size is too small, Null character can be transmitted because of the time lost to retrieve the packet size and the data address. If any bus request is immediately granted, the minimum packet size will be 6 in order to avoid Null character transmission between 2 data transmissions (at maximum TX frequency).

In TX slave mode, to ensure that the TX FIFO does not become empty, the host sends one data word at least at each 10 system clock periods. So, it prevents the Null character transmission between 2 data transmissions.

If the AHB bus is immediately granted, it will take at the most 9 system clock cycles to build a 32-bit word with 4 received 8-bit data and to store it into the host memory.

## SCOC

Ref :R&D-SOC-NT-292-V-ASTR

Issue : O rev. 2 Date : 18/06/2003

Page: 32

#### 5 ARCHITECTURE DESCRIPTION

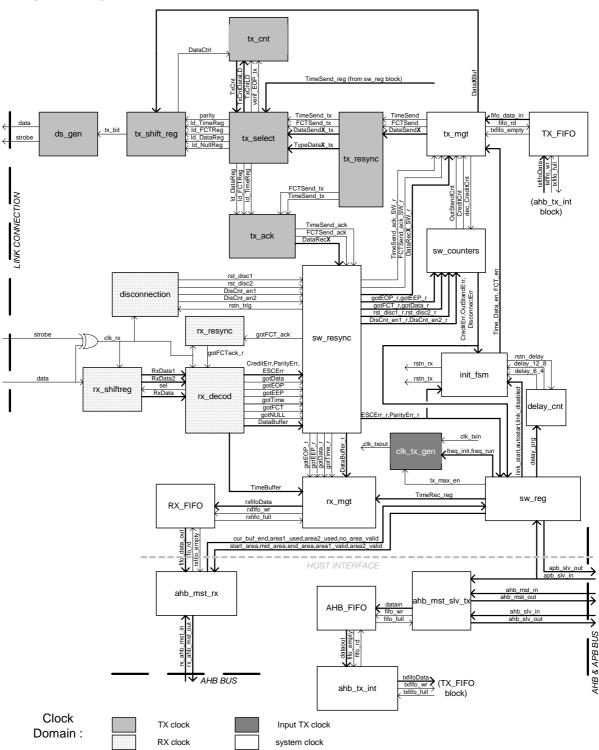

The figure below gives an overview of the SWB architecture.

Figure 3.5.8-1 global architecture

### SCOC

Ref :R&D-SOC-NT-292-V-ASTR

Issue : O rev. 2 Date : 18/06/2003

Page: 33

The above schema also describes the clock trees. The TX clock used for the transmission is made from the input TX clock. The RX clock is made from the data and strobe input signals.

#### Top input signals description:

clk\_sw : SpaceWire clock

clk\_txin : Max Tx clock

resetn : asynchronous reset

tickin\_ctm : time code to send

d\_in : data input

s\_in : strobe input

s\_in : strobe input apb\_slv\_in : APB slave tx\_ahb\_slv\_in : AHB SLAVE tx\_ahb\_mst\_in : AHB MASTER rx\_ahb\_mst\_in : AHB MASTER

test\_mode\_hard: test mode asserted by hardware

#### Top output signals description:

clk\_txout : Tx clock for test (disabled for timing performance)

tickout\_ctm : right time code received

d\_outs\_outapb\_slv\_outdata outputstrobe outputAPB slave

tx\_ahb\_slv\_out: TX AHB SLAVE tx\_ahb\_mst\_out: TX AHB MASTER rx\_ahb\_mst\_out: RX AHB MASTER err\_int: Error interrupt

nom\_int : Nominal interrupt

#### 5.1 DESCRIPTION OF THE RESET TREES

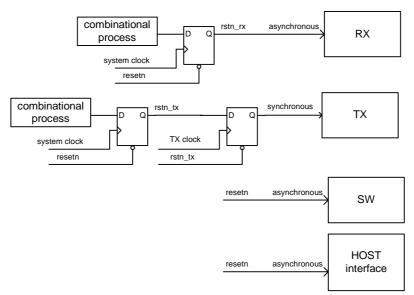

Figure 3.5.8-1 Reset trees

The RX block includes all blocks working at RX clock.

The TX block includes all blocks working at TX clock.

### SCOC

Ref :R&D-SOC-NT-292-V-ASTR

Issue : O rev. 2 Date : 18/06/2003

Page: 34

The SW and host interface blocks include all blocks working at system clock.

#### 5.2 BLOCKS WORKING AT TX CLOCK

#### 5.2.1 CLK\_TX\_GEN block

There are two different architectures for the CLK\_TX\_GEN block:

- The first one is a gated TX clock. The generated TX clock has a various frequency following the 2(n+1) frequency divider.

- The second one is a not-gated TX clock. The generated TX clock has a constant and equal frequency to the input TX clock. The use of an enable signal (clk\_tx\_en) allows the TX frequency variation. A (n+1) frequency divider is used.

The GATED\_TX\_CLK parameter selects the CLK\_TX\_GEN block architecture:

- ➤ GATED\_TX\_CLK = True : gated TX clock is used.

- ➤ GATED\_TX\_CLK = False : not-gated TX clock is used.

#### 5.2.2 DS\_GEN block

#### Input signals description

clk\_tx : clock rstn\_tx : reset DataIn : data in

#### Output signals description

D : data signal out S : strobe signal out

The goal is to generate the data and strobe signals according to the AD11 specification.

#### 5.2.3 TX\_SHIFT\_REG block

#### Input signals description

$\begin{array}{ccc} rstn\_tx & : reset \\ clk\_tx & : clock \end{array}$

LD\_TimeReg : load time code register

LD\_FCTReg : load FCT register

LD\_DataReg : load data register

LD\_NULLReg : load NULL register

TypeData1 : type data or EOP

TypeData3 : type data or EOP

TypeData4 : type data or EOP

TypeData4 : type data or EOP

parity : parity bit

tx\_mux(2:0) : mux control. Selection of the character to be serialized

TimeDataLD(7:0): time code to load

### SCOC

Ref :R&D-SOC-NT-292-V-ASTR

Issue : O rev. 2 Date : 18/06/2003

Page: 35

Data1LD(8:0) : data to load from buffer1

Data2LD(8:0) : data to load from buffer2

Data3LD(8:0) : data to load from buffer3

Data4LD(8:0) : data to load from buffer4

#### Output signals description

DataSend\_sel(1:0): data buffer select

DataCtrl : data control flag to differentiate data from EOP or EEP

tx\_bit : bit to transmit

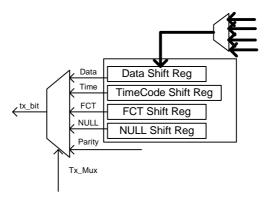

This block receives orders to load the shift registers then transmits the serial TX\_BIT signal to the DS\_GEN block.

As there are 4 data buffers (Data1LD(8:0), Data2LD(8:0), Data3LD(8:0) and Data4LD(8:0)), the block swaps from one to another each time a data is loaded. The DataSend\_sel signal indicates which data is selected.

Figure 5.2.3-1 TX shift registers

#### 5.2.4 TX\_SELECT block

#### Input signals description

rstn\_tx : reset

TimeSend\_tx : time code to send FCTSend\_tx : FCT to send

DataSend1\_tx : data from buffer1 to send

DataSend2\_tx : data from buffer2 to send

DataSend3\_tx : data from buffer3 to send

DataSend4\_tx : data from buffer4 to send

DataSend\_sel(1:0): data buffer select

TypeData1 : type data or EOP

TypeData2 : type data or EOP

TypeData3 : type data or EOP

TypeData4 : type data or EOP

TxCnt(3:0) : position of the current transmitted character

tx\_bit : TX data bit

TimeSend\_ack : TimeSend acknowledge FCTSend\_ack : FCTSend acknowledge

#### Output signals description

tx\_mux(2:0) : character select

### SCOC

Ref :R&D-SOC-NT-292-V-ASTR

Issue : O rev. 2 Date : 18/06/2003

Page: 36

TxCntDataLD(3:0) : data to load LD\_TimeReg : load time code LD\_FCTReg : load FCT LD\_DataReg : load data LD\_NULLReg : load NULL

verif\_EOP\_tx : check if data or EOP

parity : i\_parity bit TxCntLD : load txcnt

This block manages the character transmission requests from the TX\_MGT block. Following the priority order (time code > FCT > data > NULL), the TX\_SELECT block generates the appropriate load signal to the TX\_SHIFT\_REG block.

The TX\_SELECT block also activates the data or EOP/EEP check performed by the TX\_CNT. Then this block manages the TX\_CNT load.

The parity bit is computed in this block.

#### 5.2.5 TX\_CNT block

#### Input signal description

rstn\_tx : reset

TxCntLD : Load command

DataCtrl : character control bit (data or EOP/EEP) verif\_EOP\_tx : check if data or EOP to update the counter

TxCntDataLD(3:0): data to load

#### Output signal description

CntOut(3:0) : counter value

This 4-bit counter is used to count the characters length. Thus, the TX\_SLECT block can generate the load signals in appropriate time.

This counter loads the TxCntDataLD value when the TxCntLD signal is high. The counter is corrected when an EOP/EEP is checked.

#### 5.2.6 TX\_ACK block

#### Input signals description

rstn\_tx : reset

DataSend\_sel(1:0): data buffer select

FCTSend\_tx : FCT to send

LD\_FCTReg : load FCT register

LD\_DataReg : load Data register

TimeSend\_tx : time code to send

LD\_TimeReg : load time code register

#### Output signals description

DataRec1 : DataSend acknowledge for buffer1

DataRec2 : DataSend acknowledge for buffer2

DataRec3 : DataSend acknowledge for buffer3

# SCOC

Ref :R&D-SOC-NT-292-V-ASTR

Issue : O rev. 2 Date : 18/06/2003

Page: 37

DataRec4 : DataSend acknowledge for buffer4

TimeSend\_ack : TimeSend acknowledge FCTSend\_ack : FCTSend acknowledge

This block generates acknowledgement signals for the time code, FCT and data requests. The acknowledgement is activated when the corresponding shift register from the TX\_SELECT block is loaded.

The DataRec1/DataRec2/DataRec3/DataRec4 signals is activated for 4 TX clock cycles, then is automatically off after this time period.

After the activation of the TimeSend\_ack/ FCTSend\_ack signal, the deactivation is performed only when the TimeSend\_tx/ FCTSend\_tx signal is low.

#### 5.2.7 TX\_RESYNC block

# Input signals description

rstn\_tx : reset

DataSend1 : data from buffer1 to send

DataSend2 : data from buffer2 to send

DataSend3 : data from buffer3 to send

DataSend4 : data from buffer4 to send

FCTSend : FCT to send

TimeSend : Time Code to send

TypeData1 : Data or EOP

TypeData2 : Data or EOP

TypeData3 : Data or EOP

TypeData4 : Data or EOP

#### Output signals description

TypeData1\_tx : resynchronised signal

TypeData2\_tx : resynchronised signal

TypeData3\_tx : resynchronised signal

TypeData4\_tx : resynchronised signal

DataSend1\_tx : resynchronised signal

DataSend2\_tx : resynchronised signal

DataSend3\_tx : resynchronised signal

DataSend4\_tx : resynchronised signal

FCTSend\_tx : resynchronised signal

rstn\_tx\_r : resynchronised signal

TimeSend\_tx : resynchronised signal

: resynchronised signal

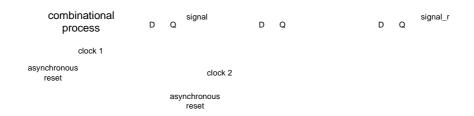

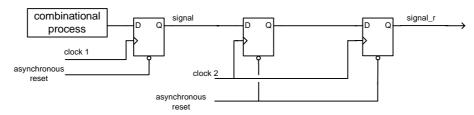

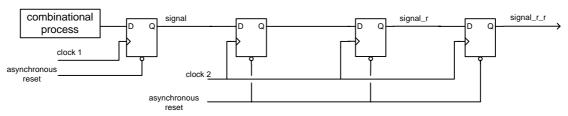

This block performs the resynchronisation of the signals from blocks working at the system clock following the below architecture.

# SCOC

Ref :R&D-SOC-NT-292-V-ASTR

Issue : O rev. 2 Date : 18/06/2003

Page: 38

#### 5.3 BLOCKS WORKING AT RX CLOCK

The RX clock is built from the DATA and STROBE signals as shown hereafter:

Data RX clock Strobe

Figure 5.2.7-1 RX clock generation

### 5.3.1 RX\_SHIFTREG block

#### Input signals description

rstn\_rx : asynchronous resetn

d : data in

sel : select RxData1 or RxData2

#### Output signals description

RxData1(9:0) : data with first bit detected on falling edge RxData2(9:0) : data with first bit detected on rising edge

RxData(9:0) : RxData1 or RxData2, depending on the NULL detection

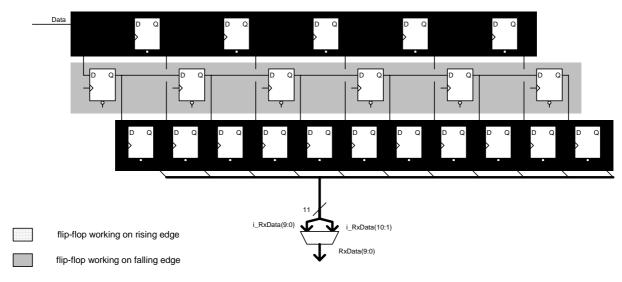

This block memorizes the input serial data on the rising and falling edge of the RX clock.